假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?插入一个流水段寄存器,得到一个两级流水线

题目

假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?插入一个流水段寄存器,得到一个两级流水线

相似考题

参考答案和解析

更多“假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟”相关问题

-

第1题:

完成一条指令的功能可以分成那两个阶段()A、取指

B、执行

C、保存

D、删除

参考答案:AB

-

第2题:

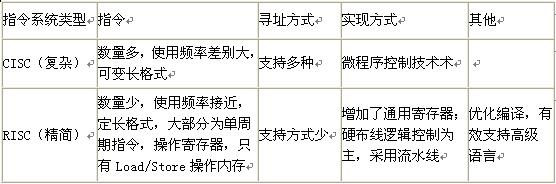

以下关于CISC(ComplexInstructionSetComputer,复杂指令集计算机)和RISC(ReducedInstructionSetComputer,精简指令集计算机)的叙述中,错误的是()。A.在CISC中,其复杂指令都采用硬布线逻辑来执行

B.采用CISC技术的CPU,其芯片设计复杂度更高

C.在RISC中,更适合采用硬布线逻辑执行指令

D.采用RISC技术.指令系统中的指令种类和寻址方式更少答案:A解析:CISC(ComplexInstructionSetComputer,复杂指令集计算机)的基本思想是,进一步增强原有指令的功能,用更为复杂的新指令取代原先由软件子程序完成的功能,实现软件功能的硬件化,导致机器的指令系统越来越庞大而复杂。CISC计算机一般所含的指令数目至少300条以上,有的甚至超过500条。RISC(ReducedInstructionSetComputer,精简指令集计算机)的基本思想是:通过减少指令总数和简化指令功能,降低硬件设计的复杂度,使指令能单周期执行,并通过优化编译提高指令的执行速度,采用硬布线控制逻辑优化编译程序。在20世纪70年代末开始兴起,导致机器的指令系统进一步精炼而简单。 -

第3题:

基本逻辑门电路有(),(),(),()利用此几种基本逻辑门电路的不同组合,可以构成各种复杂的逻辑门电路。

正确答案:“与”门;“与非”门;“或”门;“或非”门 -

第4题:

当数据流图中的某个加工的一组动作存在着多个条件复杂组合的判断时,其加工逻辑使用()。

正确答案:判定表或判定树 -

第5题:

基本逻辑门电路有()、()和(),利用此三种基本逻辑门电路的不同组合,可以构成各种复杂的逻辑门电路。

正确答案:"与"门;"或"门;"非"门 -

第6题:

假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?插入三个流水段寄存器,得到一个四级流水线

正确答案:三个流水段寄存器分别插在A和B、C和D、D和E之间,这样第一个流水段的组合逻辑延时为80ps,第二段时延为30+60=90ps,第三段时延为50ps,最后一段延时为70+10=80ps。这样每个流水段都以最长延时调整为90+20=110ps,故时钟周期为110ps,指令吞吐率为1/110ps=9.09GOPS,每条指令的执行时间为4x110=440ps。 -

第7题:

清除AX寄存器的一条逻辑指令是()或()。

正确答案:段地址;偏移地址 -

第8题:

CPU执行每一条指令都要分成若干步:取指令、指令译码、取操作数、执行运算、保存结果等。CPU在取指令阶段的操作是()

- A、从硬盘读取一条指令并放入内存储器

- B、从内存储器(或cache)读取一条指令放入指令寄存器

- C、从指令寄存器读取一条指令放入指令计数器

- D、从内存储器读取一条指令放入运算器

正确答案:B -

第9题:

组合逻辑电路的竞争-冒险是由于()引起的。

- A、电路不是最简

- B、电路有多个输出

- C、电路中存在延迟

- D、电路使用不同的门电路

正确答案:C -

第10题:

填空题清除AX寄存器的一条逻辑指令是()或()。正确答案: 段地址,偏移地址解析: 暂无解析 -

第11题:

单选题组合逻辑控制是一种硬布线控制,组合逻辑线路是其核心,它接收的输入信号不包括()A指令译码器的输出

B时序信号

C执行部件的反馈信息

DAC的运算结果

正确答案: B解析: 暂无解析 -

第12题:

单选题组合逻辑控制中,一条指令可以由一个信号逻辑表达式描述,对逻辑表达式化简后即可以用()实现。A加法器

B寄存器

C门电路

D锁存器

正确答案: C解析: 暂无解析 -

第13题:

精简指令系统RISC的特点不包括( )。A.指令数量少。优先选取使用频率最高的一些简单指令和一些常用指令,避免使用复杂指令。

B.指令的寻址方式少。通常只支持寄存器寻址方式、立即数寻址方式和相对寻址方式。

C.指令可以对主存单元中的数据直接进行处理。典型的 RISC.通常都有指令能够直接对主存单元中的数据进行处理,其执行速度较快。

D.以硬布线逻辑控制为主。为了提高操作的执行速度,通常采用硬布线逻辑(组合逻辑)来构建控制器答案:C解析:CISC系统中的指令可以对主存单元中的数据直接进行处理。典型的 CISC 通常都有指令能够直接对主存单元中的数据进行处理,其执行速度较慢。 -

第14题:

以下关于CISC(Complex Instruction Set Computer,复杂指令集计算机)和RISC(Reduced Instruction Set Computer,精简指令集计算机)的叙述中,错误的是( )。A.在CISC中,复杂指令都采用硬布线逻辑来执行

B.一般而言,采用CISC技术的CPU,其芯片设计复杂度更高

C.在RISC中,更适合采用硬布线逻辑执行指令

D.采用RISC技术,指令系统中的指令种类和寻址方式更少答案:A解析:本题考查CISC与RISC的区别,这是一种常见的考题,二者的区别如表所示。

-

第15题:

假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?吞吐量最大的流水线

正确答案:因为所有组合逻辑块中最长延时为80ps,所以,达到最大可能吞吐率的划分应该是以一个流水段延时为80ps+20ps来进行,因此,至少按五段来划分,分别把流水段寄存器插在A和B、B和C、C和D、D和E之间,这样第一段的组合逻辑延时为80ps,第二段为30ps,第三段为60ps,第四段为50ps,最后一段为70+10=80ps。这样每个流水段都以最长延时调整为80+20=100ps,故时钟周期为100ps,指令吞吐率为1/100ps=10GOPS,每条指令的执行时间为5x100=500ps。 -

第16题:

基本逻辑门电路有(),利用此三种基本逻辑门电路的不同组合,可以构成各种复杂的逻辑门电路。

正确答案:与门、或门和非门 -

第17题:

可编程序控制器的指令可分为()两类

- A、传送指令和控制指令

- B、控制指令和逻辑指令

- C、简单指令和复杂指令

- D、基本指令和扩展指令

正确答案:D -

第18题:

时序逻辑电路和组合逻辑电路最显著的区别是:()

正确答案:时序逻辑电路有记忆信息的能力而组合逻辑电路没有记忆信息的能力 -

第19题:

与精简指令计算机相反,复杂指令计算机指令较长,分成几个微指令去执行,正是如此开发程序比较容易(指令多的缘故),那么复杂指令计算机的英文简称是()。

- A、CISC

- B、RISC

- C、ARC

- D、DDR

正确答案:A -

第20题:

组合逻辑电路分析的一般步骤是()。

- A、根据逻辑图写出输出端的逻辑表达式

- B、根据需要对逻辑表达式进行变换和化简,得出最简式

- C、根据最简式列出真值表

- D、根据真值表或最简式,确定其逻辑功能

- E、根据逻辑功能画出电路图

正确答案:A,B,C,D -

第21题:

在逻辑关系比较复杂的梯形图中,常用到触点块连接指令。

正确答案:正确 -

第22题:

单选题组合逻辑电路的竞争-冒险是由于()引起的。A电路不是最简

B电路有多个输出

C电路中存在延迟

D电路使用不同的门电路

正确答案: D解析: 暂无解析 -

第23题:

填空题当数据流图中的某个加工的一组动作存在着多个条件复杂组合的判断时,其加工逻辑使用()。正确答案: 判定表或判定树解析: 暂无解析 -

第24题:

问答题假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?吞吐量最大的流水线正确答案: 因为所有组合逻辑块中最长延时为80ps,所以,达到最大可能吞吐率的划分应该是以一个流水段延时为80ps+20ps来进行,因此,至少按五段来划分,分别把流水段寄存器插在A和B、B和C、C和D、D和E之间,这样第一段的组合逻辑延时为80ps,第二段为30ps,第三段为60ps,第四段为50ps,最后一段为70+10=80ps。这样每个流水段都以最长延时调整为80+20=100ps,故时钟周期为100ps,指令吞吐率为1/100ps=10GOPS,每条指令的执行时间为5x100=500ps。解析: 暂无解析