在多级存储体系中,“cache—主存”结构的作用是解决()的问题。A、主存容量不足B、主存与辅存速度不匹配C、辅存与CPU速度不匹配D、主存与CPU速度不匹配

题目

在多级存储体系中,“cache—主存”结构的作用是解决()的问题。

- A、主存容量不足

- B、主存与辅存速度不匹配

- C、辅存与CPU速度不匹配

- D、主存与CPU速度不匹配

相似考题

更多“在多级存储体系中,“cache—主存”结构的作用是解决()的问题”相关问题

-

第1题:

三级存储体系中,主存-辅存结构是为了解决主存速度问题。()此题为判断题(对,错)。

参考答案:错误

-

第2题:

下面关于Cache的叙述,“(6)”是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是动态更新的

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

正确答案:D

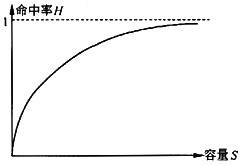

解析:本题考查高速缓存基础知识。高速缓存Cache有如下特点:它位于CPU和主存之间,由硬件实现;容量小,一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器制成;其内容是主存内容的副本,对程序员来说是透明的;Cache既可存放程序又可存放数据。Cache存储器用来动态存放主存的部分拷贝(副本)。控制部分的功能是:判断CPU要访问的信息是否在Cache存储器中,若在即为命中,若不在则没有命中。命中时直接对Cache存储器寻址。未命中时,若是读取操作,则从主存中读取数据,并按照确定的替换原则把该数据写入Cache存储器中:若是写入操作,则将数据写入主存即可。Cache的命中率主要与如下几个因素有关:程序在执行过程中的地址流分布情况;当发生Cache块失效时,所采用的替换算法;Cache的容量;在组相联映像方式中,块的大小和分组的数目;所采用的Cache预取算法等等。Cache的命中率随其容量增加而提高,它们之间的关系曲线如下图所示。在Cache容量比较小的时候,命中率提高的非常快,随着Cache容量的增加,命中率提高的速度逐渐降低。当Cache容量增加到无穷大时,命中率可望达到100%,但这是实际上是做不到的。

-

第3题:

在多级存储系统中,Cache处在CPU和主存之间,解决(55)问题。若Cache和主存的存取时间分别为T1和T2,Cache的命中率为H,则该计算机实际存取时间为(56)。当CPU向存储器执行读操作时,首先访问Cache,若命中,则从Cache中取出指令或数据,否则从主存中取出,送(57):当CPU向存储器执行写操作时,为了使Cache的内容和主存的内容保持一致,若采用(58)法,则同时写入Cache和主存。由于Cache容量比主存容量小,因此当Cache满时,执行把主存信息向Cache写入,就要淘汰Cache中已有的信息,为了提高Cache的命中率,采用一种(59)替换算法。

A.主存容量扩充

B.主存和CPU速度匹配

C.多个请求源访问主存

D.BIOS存放

正确答案:B

解析:he的主要功能是提供CPU与RAM间的速度匹配问题,存储器效率的计算公式为:HTI+(1-H)T2。为了提高Cache的命中率,我们常采用LRU最近最少使用的替换算法。 -

第4题:

在CPU和主存之间设置“Cache"的作用是为了解决( )的问题。

A.主存容量不足 B.主存与辅助存储器速度不匹配 C.主存与CPU速度不匹配 D.外设访问效率

正确答案:C

-

第5题:

计算机系统中,虚拟存储体系由()两级存储器构成。A.主存一辅存

B.寄存器一Cache]

C.寄存器一主存

D.Cache一主存答案:A解析: -

第6题:

下列有关存储器的说法错误的是()。A.访问存储器的请求是由CPU发出的

B.Cache与主存统一编址,即主存空间的某一部分属于Cache

C.Cache的功能全由硬件实现

D.Cache~主存层次主要为了解决存储系统的速度问题答案:B解析:Cache中字块保存的是主存中相应字块的副本,Cache是一种高速缓冲存储器,而不是与主存处于同等地位的存储器,故不需要占用主存空间。 -

第7题:

主存储器和CPU之间增加Cache的目的是()。

- A、解决CPU和主存之间的速度匹配问题

- B、扩大主存储器容量

- C、扩大CPU中通用寄存器的数量

- D、既扩大主存储器容量,又扩大CPU中通用寄存器的数量

正确答案:A -

第8题:

三级存储体系中,主存-缓存结构是为了解决主存速度问题。

正确答案:正确 -

第9题:

在主存储器和CPU之间增设高速缓冲存储器Cache的目的是()。

- A、扩大主存储器的容量

- B、解决CPU与主存储器之间的速度匹配问题

- C、扩大CPU中通用寄存器的数量

- D、既扩大主存储器的容量又扩大CPU中通用寄存器的数量

正确答案:B -

第10题:

在PC机中,各类存储器的速度由高到低的次序是()。

- A、主存、Cache、硬盘、软盘

- B、硬盘、Cache、主存、软盘

- C、Cache、硬盘、主存、软盘

- D、Cache、主存、硬盘、软盘

正确答案:D -

第11题:

单选题多级存储系统由cache、()和外存组成。A内存

B主存

C硬盘

D光盘

正确答案: D解析: 暂无解析 -

第12题:

单选题主存储器和CPU之间增加Cache的目的是( )。A解决CPU和主存之间的速度匹配问题

B扩大主存储器容量

C扩大CPU中通用寄存器的数量

D既扩大主存储器容量,又扩大CPU中通用寄存器的数量

正确答案: A解析:

CPU的速度是主存储器的数十倍,需要Cache匹配两者的速度。Cache对CPU是透明的,CPU看不到Cache所进行的操作,所以增加Cache不是为了扩大通用寄存器的数量。 -

第13题:

三级存储体系中,主存-缓存结构是为了解决主存速度问题。()此题为判断题(对,错)。

参考答案:正确

-

第14题:

关于Cache(高速缓冲存储器)的说法中,错误的是(9)。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

正确答案:D

解析:本题考查高速缓存基础知识。高速缓存Cache有如下特点:它位于CPU和主存之间,由硬件实现;容量小,一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器制成;其内容是主存内容的副本,对程序员来说是透明的;Cache既可存放程序又可存放数据。Cache存储器用来存放主存的部分拷贝(副本)。控制部分的功能是:判断CPU要访问的信息是否在Cache存储器中,若在即为命中,若不在则没有命中。命中时直接对 Cache存储器寻址。未命中时,若是读取操作,则从主存中读取数据,并按照确定的替换原则把该数据写入Cache存储器中:若是写入操作,则将数据写入主存即可。Cache的命中率主要与如下几个因素有关:程序在执行过程中的地址流分布情况:当发生Cache块失效时,所采用的替换算法:Cache的容量:在组相联映像方式中,块的大小和分组的数目;所采用的Cache预取算法等。Cache的命中率随它的容量的增加而提高,它们之间的关系曲线见下图所示。在 Cache容量比较小的时候,命中率的提高得非常快,随着Cache容量的增加,命中率提高的速度逐渐降低。当Cache容量增加到无穷大时,命中率可望达到100%,但这实际上是做不到的。

-

第15题:

在计算机系统中,以下关于高速缓存 (Cache) 的说法正确的是( )。

A.Cache的容量通常大于主存的存储容量B.通常由程序员设置Cache的内容和访问速度C.Cache 的内容是主存内容的副本D.多级Cache 仅在多核cpu中使用

正确答案:C

-

第16题:

在多级存储体系中,"Cache-主存"结构的作用是解决 ( ) 的问题。A.辅存与CPU速度不匹配

B.主存与CPU速度不匹配

C.主存容量不足

D.主存与辅存速度不匹配答案:B解析:本题考查Cache的作用。高速存储器能以极高的速率进行数据的访问,但因其价格高昂,如果计算机的主存储器完全由这种高速存储器组成则会大大增加计算机的成本。为了很好地解决主存与CPU速度不匹配的这个问题,采用了"Cache-主存"结构,即在主存与CPU之间增加一层小容量的高速存储器Cache。这利用了程序的局部性原理。 -

第17题:

在主存储器和CPU之间增加Cache的目的是______。A.解决CPU和主存之间的速度匹配问题

B.扩大主存储器容量

C.扩大CPU中通用寄存器的数量

D.既扩大主存储器容量,又扩大CPU中通用寄存器的数量答案:A解析:本题考查计算机体系结构方面的基础知识。高速缓冲存储器(Cache)是存在于主存与CPU之间的一级存储器,由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多,接近于CPU的速度。它和主存储器一起构成一级的存储器。高速缓冲存储器和主存储器之间信息的调度和传送是由硬件自动进行的。在计算机技术发展过程中,主存储器存取速度一直比中央处理器操作速度慢得多,使中央处理器的高速处理能力不能充分发挥,整个系统的工作效率受到影响。有很多方法可用来缓和中央处理器和主存储器之间速度不匹配的矛盾,如采用多个通用寄存器、多存储体交叉存取等,在存储层次上采用高速缓冲存储器也是常用的方法之一。很多大、中型计算机以及新近的一些小型机、微型机也都采用高速缓冲存储器。根据程序局部性原理,正在使用的主存储器某一单元邻近的那些单元将被用到的可能性很大。因而,当中央处理器存取主存储器某一单元时,计算机硬件就自动地将包括该单元在内的那一组单元内容调入高速缓冲存储器,中央处理器即将存取的主存储器单元很可能就在刚刚调入到高速缓冲存储器的那一组单元内。于是,中央处理器就可以直接对高速缓冲存储器进行存取。在整个处理过程中,如果中央处理器绝大多数存取主存储器的操作能为存取高速缓冲存储器所代替,计算机系统处理速度就能显著提高。 -

第18题:

下面是主存储器和CAChe的比较,正确的有()

- A、微机主存储器多数采用半导体动态存储器(DRAM),CAChe采用半导体静态存储器(SRAM)。这两种存储器中的信息均不能长期保留

- B、CPU访问主存储器的速度快于访问CAChe的速度

- C、在配有CAChe的计算机中,CPU每次访问存储器都首先访问CAChe,若欲访问的数据在CAChe中,则访问结束,否则,再访问主存储器,并把有关数据取人CAChe

- D、CAChe容量一般都小于主存储器

正确答案:A,C,D -

第19题:

多级存储系统由cache、()和外存组成。

- A、内存

- B、主存

- C、硬盘

- D、光盘

正确答案:B -

第20题:

三级存储体系中,主存-辅存结构是为了解决主存速度问题。

正确答案:错误 -

第21题:

在多级存储体系中,“cache—主存”结构的作用是解决()的问题。

- A、主存容量不足

- B、主存与辅存速度不匹配

- C、辅存与CPU速度不匹配

- D、主存与CPU速度不匹配

正确答案:D -

第22题:

判断题三级存储体系中,主存-缓存结构是为了解决主存速度问题。A对

B错

正确答案: 错解析: 暂无解析 -

第23题:

单选题在多级存储体系中,“cache--主存”结构的作用是解决()的问题。A主存容量不足

B主存与辅存速度不匹配

C辅存与CPU速度不匹配

D主存与CPU速度不匹配

正确答案: B解析: 暂无解析 -

第24题:

单选题在多级存储体系中,“cache—主存”结构的作用是解决()的问题。A主存容量不足

B主存与辅存速度不匹配

C辅存与CPU速度不匹配

D主存与CPU速度不匹配

正确答案: D解析: 暂无解析